| Biologie | Chimie | Didactica | Fizica | Geografie | Informatica |

| Istorie | Literatura | Matematica | Psihologie |

Synchronous

Aceasta sectiune a manualului contine urmatoarele elemente:

1 Introducere

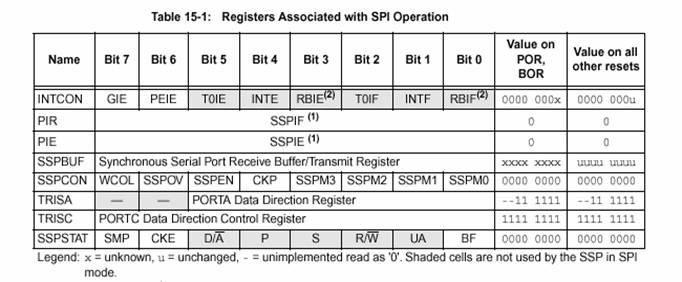

2 Registrii de control

3 Modul SPI

4 Operatiile SSP I2C

5 Initializarea

6 Indicii pentru design

7 Note de aplicatii

1 Introducere

Modulul Port Serial Sincron (SSP) este o interfata seriala folosita la comunicarea perifericele sau cu alte microcontrollere.Aceste periferice pot fi si EEPROM-uri seriale,registre de deplasare,drivere pentru display,convertoare A/D,etc.Modulul SSP poate opera in doua moduri:

Serial Peripheral Interface (SPI)

Inter_Integrated Circuit (I2C)

Mod Slave

Control I/O in panta,si detectie bit de start si stop pentru implementarea software mai usoara a modurilor Master si Multi-Master.

2 Registrii de control

bit 7 SMP: momentul esantionarii datei de intrare a SPI

1 = data de intrare este esantionata la sfarsitul duratei

0 = data de intrare este esantionata la mijlocul duratei

SMP trebuie resetat cand SPI lucreaza in modul slave

bit 6 CKE: Selectia frontului de clock pentru SPI

CKP = 0 (SSPCON<4>)

1 = data este transmisa pe frontul crescator al SCK

0 = data este transmisa pe frontul descrescator al SCK

CKP = 1 (SSPCON<4>)

1 = data este transmisa pe frontul descrescator al SCK

0 = data este transmisa pe frontul crescator al SCK

bit 5 D/A: bitul Data/Adresa (numai in modul I2C )

1 = indica ca ultimul octet receptionat sau transmis este data

0 = indica ca ultimul octet receptionat sau transmis este adresa

bit 4 P: Stop bit

(Numai in modul I2C. Acest bit este resetat cand modulul SSP este dezactivat)

1 = indica ca un bit de stop a fost anterior detectat (acest bit este 0 la RESET)

0 = bitul de stop nu a fost anterior detectat

bit 3 S: Start bit

(Numai in modul I2C. Acest bit este resetat cand modulul SSP este dezactivat)

1 = indica ca un bit de start a fost anterior detectat (acest bit este 0 la RESET)

0 = bitul de start nu a fost anterior detectat

bit 2 R/W: bitul de informatie Read/Write (numai in modul I2C)

Acest bit contine informatia R/W corespunzatoare ultimei potriviri de adresa.Acest bit este valid pornind de la stabilirea adresei pana la urmatorul bit de start , de stop sau NACK(not acknowledge).

1 = Read

0 = Write

bit 1 UA: Update Address-actualizare adresa (numai in modul I2C pe 10 biti)

1 = indica ca userul trebuie sa actualizeze adresa din registrul SSPADD

0 = nu este necesara actualizarea adresei

bit 0 BF: bitul de stare Buffer Full

Receptie (modurile SPI si I2C)

1 = receptie terminata SSPBUF este plin

0 = receptie neterminata SSPBUF este gol

Trnasmisie (numai in modul I2C)

1 = transmisie in progres,SSPBUF este plin

0 = transmisie completa,SSPBUF este gol

Legenda

Registrul SSPCON : Synchronous

Register

bit 7 WCOL: Write Collision Detect bit (bitul de detectie coliziune la scris )

1 = registrul SSPBUF este scris in timp ce inca transmite cuvantul anterior

(trebuie resetat software)

0 = fara coliziunu

bit 6 SSPOV: Receive Overflow Indicator bit(bitul indicator de overflow la receptie)

In modul SPI :

1 = un nou octet este receptionat in timp ce SSPBUF inca detine data anterioara.

In caz de overflow , data din registrul SSPSR este pierduta si SSPBUF nu mai este actualizat.Overflow poate apare doar in modul slave.Userul trebuie sa citeasca SSPBUF , chiar daca doar se transmit date pentru a evita setarea bitului de overflow.

In modul master bitul de overflow nu este setat deoarece fiecare noua receptie (si transmisie) este initiata prin scrierea registrului SSPBUF.

0 = fara overflow

In modul I2C:

1 = un octet este receptionat in timp ce registrul SSPBUF inca detine data anterioara.

SSPOV este un bit 'don't care'(indiferent) in modul de transmisie.SSPOV trebuie resetat software in oricare mod de lucru.

0 = No overflow

bit 5 SSPEN: Synchronous Serial Port Enable bit(bitul de activare a portului serial sincron)

In ambele moduri , cand este activat , acesti pini trebuie configurati ca intrari sau iesiri.

In modul SPI :

1 = activeaza portul serial si configureaza

0 = dezactiveaza portul serial si configureaza acesti pini ca pini de port I/O

In modul I2C:

1 = activeaza portul serial si configureaza pinii SDA si SCL ca sursa a pinilor portului serial.

0 = dezactiveaza portul serial si configureaza acesti pini ca pini de port I/O

bit 4 CKP: Clock Polarity Select bit(bitul de selectie a polaritatii clockului)

In modul SPI :

starea idle pentru clock este nivelul high

0 = starea idle pentru clock este nivelul low

In modul I2C :

Control pentru eliberarea SCK:

1 = activeaza clock

0 = tine clockul pe low (folosit pentru a asigura timpul de setup al datelor)

bit 3:0 SSMP3:SSMP0

(biti de selectie a modului de lucru a portului serial sincron)

0000 = SPI mod master, clock = FOSC/4

0001 = SPI mod master, clock = FOSC/16

0010 = SPI mod master, clock = FOSC/64

0011 = SPI mod master, clock = TMR2 output/2

0100 = SPI mod slave , clock = pinul SCK . Activare control prin pinul SS.

0101 = SPI mod slave, clock = pinul SCK . Dezctivare control prin pinul SS.

. Pinul SS poate fi folosit ca pin de intrare/iesire.

0110 = I2C modul slave, adresa pe 7 biti

0111 = I2C modul slave, adresa pe 10 pe biti

1000 = Rezervat

1001 = Rezervat

1010 = Rezervat

1011 = mod master I2C controlat prin firmware

1100 = Rezervat

1101 = Rezervat

1110 = I2C mod slave ,adrese pe 7 biti cu intreruperi de bit de start si stop activate.

1111 = I2C mod slave, adrese pe 7 biti cu intreruperi de bit de start si stop activate.

Legenda

3 Modul SPI

Modul SPI permite ca 8 biti de date sa fie sincron transmisi si receptionati simultan.Toate cele 4 moduri ale SPI sunt suportate, ca si Microwire cand SPI este in modul master.

Pentru a realiza comunicarea se folosesc urmatorii pini:

Serial Data Out (SDO)

Serial Data In (SDI)

Serial Clock (SCK )

In plus se mai poate folosi si un al patrulea bit in modul slave:

Slave Select (SS)

3.1 Operatii

La initializarea SPI trebuie specificate cateva elemente.Acest lucru se realizeaza prin programarea bitilor de control corespunzatori din registrul SSPCON (SSPCON <5:0>)

si SSPSTAT<7:6>.

Acesti biti de control permit specificarea urmatoarelor elemente:

. Mod Master (SCK este iesirea de clock)

. Mod Slave (SCK este intrarea de clock)

. Polaritate Clock (starea idle a SCK)

. Frontul clockului (data la iesire pe frontul crescator /descrescator al clockului)

. Momentul de esantionare a datei de intrare

. Rata clock (doar in mod Master)

. Selectare mod Slave (doar in modul Slave)

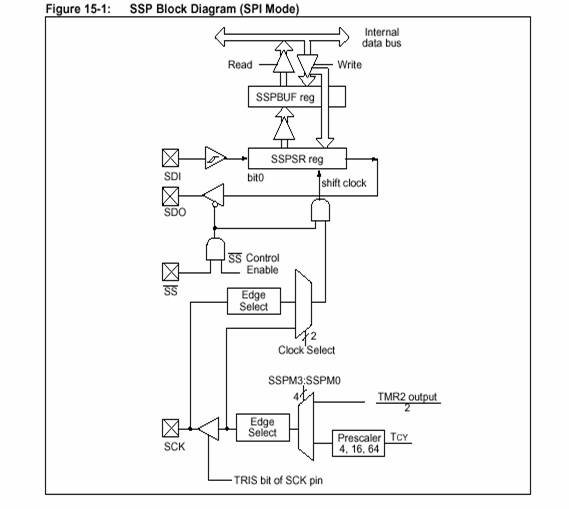

Figura 15-1 arata diagrama modulului SSP, in modul SPI.

SSP contine un registru de deplasare (SSPSR) si un registru buffer(SSPBUF) .

SSPSR deplaseaza data in/afara din dispozitiv,primul fiind cel mai semnificativ bit.

SSPBUF detine data care a fost scrisa in SSPSR pana cand data receptionata este gata.

Odata ce cei 8 biti de date au fost receptionati , octetul este mutat in registrul SSPBUF.

Apoi bitul care detecteaza buffer full (BF) (SSPSTAT<0>) si flagul de intrerupere suntsetati .Aceasta dubla bufferare a datei receptionate pemite ca pentru urmatorul octet sa se inceapa receptia inaintea citirii datei care tocmai a fost primita.

Orice scriere in registrul SSPBUF in timpul transmisiei/receptiei va fi ignorata,si bitul de detectie a coliziunii WCOL (SSPCON <7>)va fi setat.Software-ul utilizatorului trebuie sa reseteze bitul WCOL astfel incat sa se poata determina daca scrierile care urmat s-au incheiat cu succes.

Cand a aplicatia software asteapta sa primeasca date valide SSPBUF trebuie citit inainte de scrierea in SSPBUF a urmatorului octet de transferat.Bitul care indica buffer full (BF)(SSPSTAT<0>) indica cand SSPBUF a fost incarcat cu data receptionata (transmisia s-a incheiat).Cand SSPBUF este citit , bitul BF este resetat.Aceste date pot fi nerelevante daca SPI este doar transmitator.In general intreruperea SSP este folosita pentru a determina cand transmisia/receptia s-a incheiat.SSPBUF trebuie scris sau citit.

Daca nu se foloseste sistemul de intreruperi , interogarea software poate fi folosita pentru a se evita coliziunile.Exemplul 15-1 arata modul de incarcare a SSPBUF (SSPSR)pentru transmitere date.

BCF STATUS, RP1 ;specifica bancul

BSF STATUS, RP0 ;

LOOP BTFSS SSPSTAT, BF ;A fost data primita(transmisie completa)?

GOTO

BCF STATUS, RP0 ;specifica bancul1

MOVF SSPBUF, W ;W reg = continutul lui SSPBUF

MOVWF RXDATA ;salvez in RAM daca data are o insemnatate

MOVF TXDATA, W ;W reg = contiunutul lui TXDATA

MOVWF SSPBUF ;noua data de transmis

SSPSR nu poate fi citit/scris direct si poate fi accesat doar adresand registrul SSPBUF.

In plus registrul de stare al SSP (SSPSTAT) contine mai multi indicatori de conditie.

3.2 Activarea SPI I/O

Pentru activarea portului serial bitul de activare a SSP ,SSPEN(SSPCON <5>) trbuie setat.Pentru resetarea sau reconfigurarea modului SPI,se reseteaza bitul SSPEN care reinitializeaza registrul SSPCON si apoi se seteaza bitul SSPEN.Aceasta secventaconfigureaza pinii SDI,SDO,SDK si SS ca pini de port serial.

Pentru a pinii sa se comporte ca pini de port serial,trebuie ca bitii pentru directia datei (registrul TRIS)sa fie programati dupa cum urmeaza:

. SDI bitul TRIS setat

. SDO bitul TRIS resetat

. SCK (Mod Master) bitul TRIS resetat

. SCK (Mod Slave) bitul TRIS setat

.SS bitul TRIS setat

Orice functie a portului serial care nu este dorita poate fi suprascrisa programand bitii pentru directia datelor in mod coresounzator(cu valori opuse).Un exemplu ar fi cel din modul master unde doar se transmit date (la un driver de display),in acest caz SDI si SS ar putea fi folositi ca iesiri resetand bitii corespunzatori din TRIS.

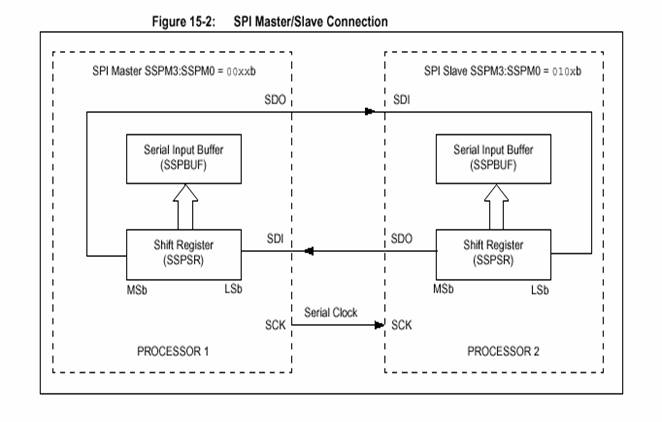

3.3 Conectari tipice

(Processor 1) initiaza transferul de date prin trimiterea semnalului SCK.Data este deplasata din ambele registre de deplasare pe frontul anterior programat,si este memorata

pe frontul specificat de bitul SMP.Ambele procesoare ar trebuie programate la aceeasi polaritate a clockului si apoi ambele controllere vor transmite si receptiona date in acelasi timp.Daca data are sens (date "dummy") sau nu depinde de aplicatia sofware.

Acest lucru duce la trei scenarii pentru transmiterea datelor:

. Master-ul trimite date - Slave-ul trimite date "dummy"

. Master-ul trimite date - Slave-ul trimite date

. Master-ul trimite date "dummy" - Slave-ul trimite date

3.4 Operatiile master-ului

Masterul determina cand slave-ul (Processor2)trebuie sa transmita date prin protocolul software.

In modul master data este transmisa si receptionata imediat ce SSPBUF a fost inscris.

Daca SPI doar primeste date , iesirea SDO ar putea fi dezactivata (programata ca intrare).Registrul SSPSR va continua sa citeasca data prezenta pe pinul SDI la rata de clock programata.Fiecare octet primit va fi incarcat in SSPBUF ca si cum ar fi un octet receptionat normal (biti de intrerupere si de stare setati corepunzator).Acest lucru ar putea fi util in aplicatii de receptie date in modul de monitorizare a activitatii pe linie.

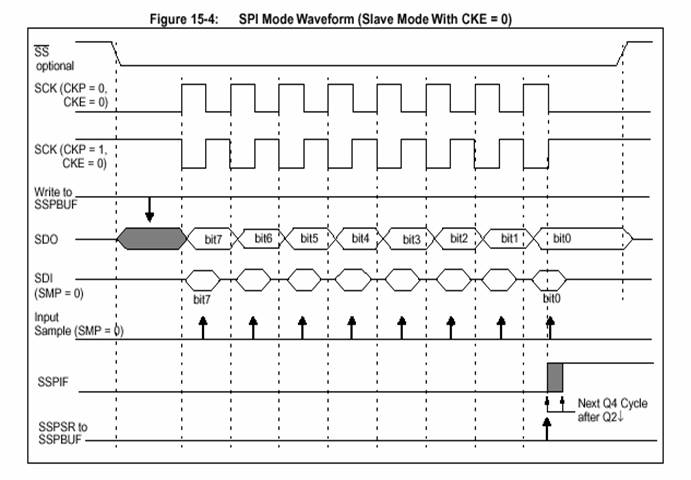

Polaritatea clock-ului este selectata prin setarea corespunzatoare a bitului CKP(SSPCON<4>).Formele de unda ar arata ca in figura 15-3 ,15-4 si 15-5 unde MSB este treansmis la inceput.In modul master , clock-ul SPI poate fi:

.FOSC/4 (sau TCY)

.FOSC/16 (sau 4 . TCY)

.FOSC/64 (sau 16 . TCY)

. Timer2 iesirea/2

Aceasta permite un data rate maxim de 5 Mbps (la

20 MHz).

3.5 Operatiile slave

Cand ultimul bit este memorat , flagul de intrerupere SSPIF este setat.

Polaritatea clock-ului este selectata prin programarea bitului CKP (SSPCON <4>).

In modul sleep , slave-ul poate transmite si receptiona date .Cand un octet este recxeptionat,dispozitivul va iesi din modul sleep,daca intreruperea este activata.

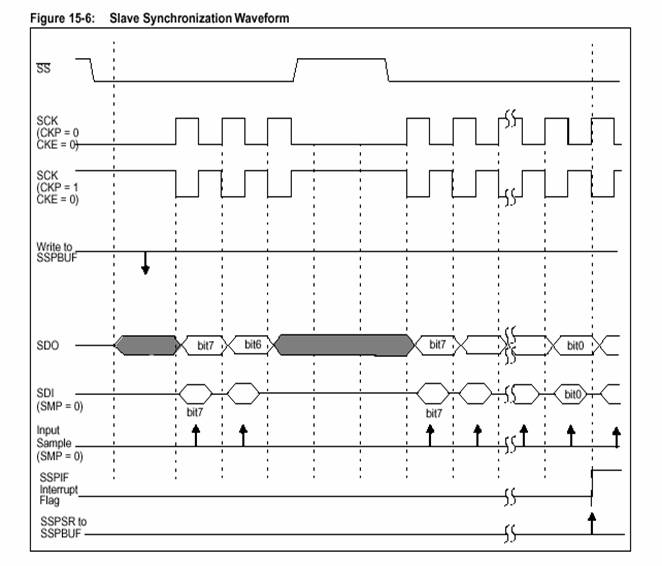

3.6 Modul de selectie a slave-ului

In modul de selectie a slave-ului , pinul SS permite mai multi slave si un singur master.

SPI trebuie sa fie in modul slave (SSPCON<3:0>=04h)si bitul TRIS pentru pinul SS,trebuie sa fie setat pentru modul de selectie slave pentru a fi activat.

Cand pinul SS este 0 logic transmisia si receptia sunt permise.Cand SS devine 1 logic SDO este trecut in inalta impedanta.Rezistente de pull-up sunt de dorit in aceste cazuri.

Cand SPI este in mod slave si cotrolul pinului SS este activat (SSPCON<3:0>=0100) modulul SPI va fi resetat daca SS este legat la VDD.Daca SPI este folosit in modul Slave cu bitul CKE setat atunci controlul pinului SS trebuie activat.

Cand modulul SPI este resetat ,bitul counter este fortat la 0.Acest lucru poate fi facut fie fortand SS la nivel 1 logic sau resetand SSPEN(figura 15-6).

Pentru a simula comunicatia cu 2 fire ,SDO poate fi conectat la pinul SDI.

Cand SPI opereaza ca receptor SDO poate fi configurat ca intrare.Acest lucru dezactiveaza transmisia de la SDO.SDI poate fi lasat ca iesire ,deoarece nu poate crea un conflict pe bus.

3.7 Operatiile sleep

In modul master toate clock-urile sunt oprite si transmisia / receptia vor ramane in

starea respectiva pana cand dispozitivul iese din modul sleep.

Dupa ce dispozitivul se intoarce in starea normala modulul va continua sa transmita/receptioneze date.

In modul slave , registrul SPI de deplasare opereaza asincron .Acest lucru permite ca dispozitivul sa intre in modul sleep si data sa fie deplasata in registrul de deplasare SPI.Cand toti cei 8 biti au fost primiti ,flagul de intrerupere SSP va fi setat si daca este permis acest lucru dispozitivul v fi scos din starea de sleep.

When all 8-bits have been received, the SSP interrupt flag bit will be set and if

enabled will wake the device from sleep.

3.8 Efectele RESET

Un reset dezactiveaza modulul SSP si incheie transferul curent.

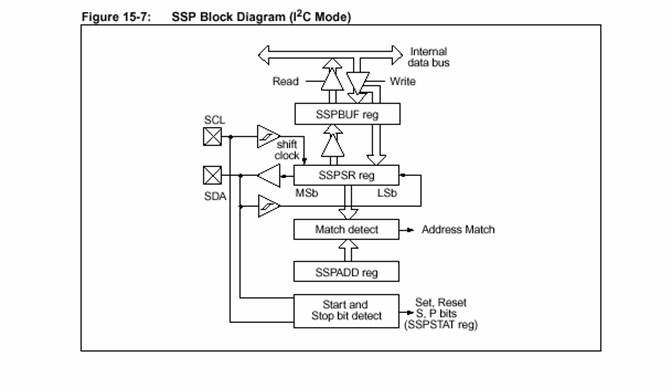

4 Operatiile SSP I2C

Modulul SSP in modul I2C implementeaza toate functiile slave , cu exceptia apelului genera si permite intreruperi la bitii de start si stop pentru a facilita implementarile software a functiilor master.Modulul SSP implementeaza specificatiile standard cat I adresarea pe 7 si 10 biti.

Doi pini sunt folositi pentru transferul de date.Acestia sunt SCL , care este clockul

si SDA, care este data.Mai multe detalii in AppendixA.Utilizatorul trebuie sa configureze acesti pini ca intrari prin intermediul registrului TRIS.Functiile modulului SSP sunt activate setand SSPEN (SSPCON<5>).

Un filtru pentru paraziti functioneaza pentru SDA si SCL .Acest filtru opereaza in gama 100KHz - 400Khz.

D

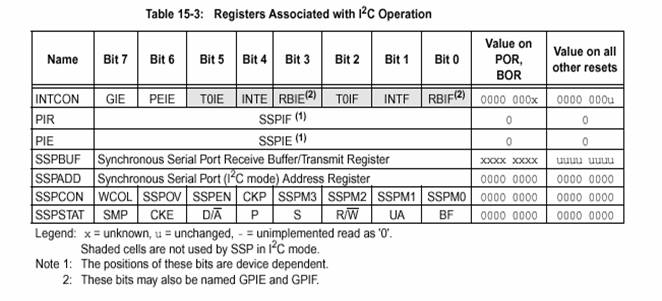

Modulul SSP are 5 registrii pentru opertii I2C.Acestia sunt:

. SSP Control Register (SSPCON)

. SSP Status Register (SSPSTAT)

. Serial Receive/Transmit Buffer (SSPBUF)

. SSP Shift Register (SSPSR) - Not directly accessible

. SSP Address Register (SSPADD)

Registrul SSPCON permite controlul opertiilor I2C.Patru biti de selectie a modului de lucru (SSPCON<3:0>) permit alegerea unuia din urmatoarele moduri de lucru:

.I2C Mod Slave (adresa 7-biti)

.I2C Mod Slave (adresa 10-biti)

.Mod I2C Multi-Master controlat prin Firmware (intreruperile de start si stop activate)

.Mod Master I2C controlat prin Firmware , slave este idle

Inainte de selectarea modului I2C ,SCL si SDA trebuie progrmate ca intrari prin intermediul TRIS.Selectarea unui mod I2C prin setarea SSPEN permite ca SCL si SDA

sa fie folosite ca linii de clock si date in modul I2C.

Registrul SSPSTAT da starea transferului de date.

Aceasta informatie include detectia bitului de start si stop,specifica daca data receptionata este data sau adresa,daca urmatorul octet este completarea unei adrese de 10 biti si daca transferul este de tip read sau write.

SSPBUF este registrul din care se citeste sau scrie data .SSPSR deplaseaza data in interior sau exterior.In operatiile de receptie SSPBUF si SSPSR formeaza un buffer dublu.Acesta permite ca receptia urmatorului octet sa inceapa inainte de citirea ultimului octet primit.Cand un octet complet este receptionat este transferat in SSPBUF si este setat flagul SSPIF.Daca un alt octet complet este receptionat inainte ca SSPBUF sa fie citit ,apare overflow la receptorsi bitul SSPOV (SSPCON<6>) este setat si octetul din SSPSR este pierdut.

Registrul SSPADD contine adresa slave-ului.In modul de adresare cu 10 biti,utilizatorul trebuie sa scrie ovctetul superior al adresei (1111 0 A9 A8 0).Dupa inscrierea octetului superior trebuie inscris octetul inferior(A7:A0).

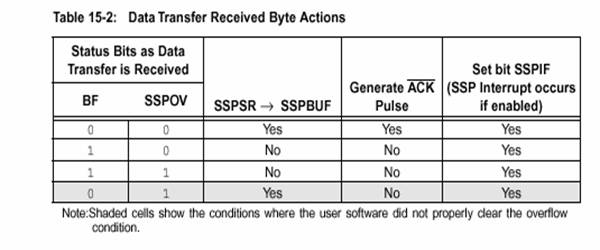

4.1 Modul Slave

Cand adresa primita este aceeasi cu cea proprie se va genera automat un puls de acknowledge (ACK)si apoi se va incarca SSPBUF cu valoarea primita care se afla in registrul SSPSR.

Exista cateva conditii in care modulul SSP nu va genera ACK:

Bitul BF (SSPSTAT<0>) a fost setat inainte de terminarea mesajului.

Bitul de overflow ,SSPOV(SSPCON <6>) a fost setat inainte de terminarea mesajului.

In acest caz valoarea din SSPSR nu va fi incarcata in SSPBUF,dar bitii SSPIF si SSPOV sunt setati.

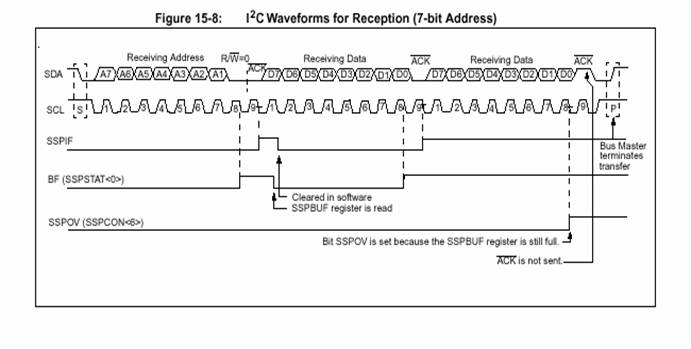

Tabelul 15-2 arata ce se intampla cand un octet este receptionat dandu-se starea bitilor BF si SSPOV.Casutele colorate arata conditiile cand software-ul nu a eliminat conditia de overflow.

Bitul BF este resetat prin citirea SSPBUF in timp ce SSPOV este resetat prin software.

Clock-ul SCL trebuie sa garanteze durata minima a perioadelor de 1 si 0 logic.

4.1.1 Adresarea

Odata ce modulul SSP a fost activat ,asteapta o conditie de start .

Dupa conditia de start cei 8 biti sunt deplasati in SSPSR.Toti bitii care sosesc sunt esantionati pe frontul crescator al SCL.Valoarea registrului SSPSR<7:1> este comparata cu valoarea din SSPADD.Adresele sunt comparate pe frontul descrescator al celui de-al optulea clock.Daca adresele se potrivesc ,BF si SSPOV sunt resetati si urmatoarele evenimente apar:

a)valoarea registrului SSPSR este incarcata in SSPBUF pe frontul descrescator al SCL.

b)BF este setat pe frontul descrescator al celui de-al optulea puls SCL .

c)Un puls de confirmare (ACK)este generat.

d)SSPIF este setat (inreruperea este generata daca este permis) pe frontul descrescator al celui de-al noualea puls SCL.

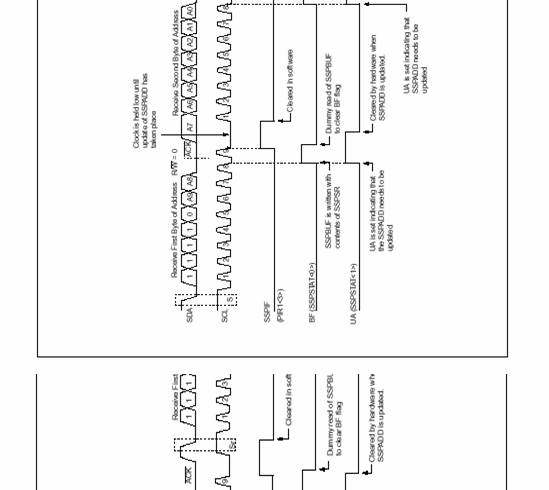

In module de adresare pe 10 biti ,doi octeti sunt necesari pentru a fi receptionati de catre slave.Cei mai semnificativi 5 biti din primul octet specifica daca este o adresa pe 10 biti.

Bitul de R/W (SSPSTAT<2>)trebuie sa specifice o scriere astfel incat slave-ul sa primeasca si cel de-al doilea octet de adresa.

Pentru adresele pe 10 biti primul octet este egal cu '1111 0 A9 A8 0' , unde A9 si A8 sunt cei mai semnificativi biti ai adresei.

Secventa de evenimente pentru adresele pe 10 biti este urmatoarea,cu pasii 7:9 pentru

Slave-transmitator.

1. Se receptioneaza intai primul octet al adresei (SSPIF, BF si UA (SSPSTAT<1> sunt setati)

2.Se actualizeaza SSPADD cu cel de-al doilea octet al adresei (se reseteaza UA si se elibereaza linia SCL)

3.Se citeste SSPBUF (se reseteaza BF) si se reseteaza SSPIF.

4.Se receptioneaza ce de-al doilea octet al adresei (SSPIF,BF,UA sunt setati)

5. Se actualizeaza SSPADD cu octetul superior al adresei.Se reseteaza UA si se elibereaza SCL.

6. Se citeste SSPBUF (se reseteaza BF) si se reseteaza SSPIF.

7.Se primeste conditia de start repetat.

8.Se reptioneaza mai intai primul octet al adresei(SSPIF si BF sunt setati)

9.Se citeste SSPBUF (se reseteaza Bf) si se reseteaza SSPIF.

Nota: Dupa conditia de start repetat(pasul 7) in modul de adresare pe 10 biti ,utilizatorul

trebuie sa trimita doar primii 7 biti ,el nu trebuie sa actualizeze a doua jumatate a adresei.

4.1.2 Receptia

Din SSPSTAT este resetat.Adresa receptionata este incarcata in SSPBUF .Cand aparae un overflow pentru octetul de adresa nu se genereaza un ACK.O conditie de overflow este definita fie prin BF (este setat) fie prin SSPOV (este setat).Deci cand un octet este primit ,cu aceste conditii,si se incearca mutarea lui din SSPSR in SSPBUF nu este generat ACK.

O intrerupere SSP este generata pentru fiecare octet de date transferat.SSPIF trebuie resetat prin software.SSPSTAT este folosit pentru a determina starea octetului receptionat.

4.1.3 Transmisia

Cand bitul R/W din octetul de adresa este setat si apare o potrivire de adresa,bitul R/W din registrul SSPSTAT este setat.Adresa receptionata este incarcata in registrul SSPBUF.

ACK va fi trimis pe cel de-al noualea bit ,si SCL este tinut pe nivel 0 logic.Data de transmis trebuie incarcata in registrul SSPBUF ,care incarca deasemenea registrul SSPSR.Apoi SCL ar trebui activat prin setarea bitului CKP(SSPCON<4>).

Mater-ul trebuie sa monitorizeze SCL inainte de a trimite un nou puls de clock.

Dispozitivele slave pot intarzia master-ul prin punerea liniei de clock la nivel 0 logic.

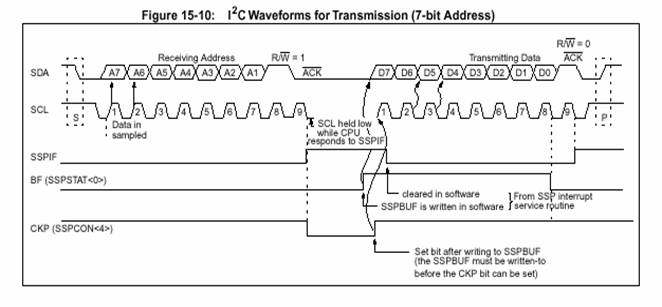

Cei 8 biti de date sunt deplasati pe frontul descrescator al SCL.Aceasta asigura ca SDA este valid in timpul cat SCL este pe 1 logic.(figura 15-10)

O intrerupere SSP este generata pentru fiecare octet data de transferat.SSPIF trebuie resetat prin software, SSPSTAT este folosit pentru a determina starea transferului de date. SSPIF este setat pe frontul descrescator al celui de-al noulea puls SCL.

In cazul slave-transmitator ,ACK de la master-receptor este memorat pe frontul crescator al celui de-al noualea puls pe SCL.Daca linia SDA era pe 1 logic (not ACK),atunci transferul este complet.

Cand not ACK este memorat de slave , logica slave-ului este resetata si apoi slave-ul monitorizeaza aparitia unui bit de START.Daca SDA era pe nivel 0 logic ,data este incarcata in SSPBUF ,care incarca si SSPSR.Apoi linia SCL trebuie activata

prin setarea bitului CKP.

4.1.4 Arbitrarea clock-urilor

4.2 Modul Master (Firmware)

Modul master este suportat prin generarea de intreruperi la detectia conditiilor de start si stop.Bitii de start si stop sunt resetati prin reset sau cand SSP este dezactivat.Controlul busului I2C poate fi preluat cand bitul P(START) este setat,sau bus-ul este idle cu ambii biti de start si stop resetati.

In modul master SCL si SDA sunt manipulate resetand bitii corespunzatori din TRIS.Nivelul iesirii este intotdeauna low.

Deci cand se transmit date , un bit de 1 trebuie sa aiba bitul corespunzator setat(intrare) si un bit de 0 trebuie sa aiba bitul resetat(iesire).Acelasi scenariu se aplica si la SCL cu registrul TRIS.

Urmatoarele evenimente vor cauza setarea lui SSPIF:

. conditie de START

. conditie de STOP

. octet de data transmis/receptionat

Modul master poate fi realizat fie cu modul slave idle (SSPM3:0=1011)

Fie cu slave active (SSMP3:0=1110saun 1111).Cand modurile slave sunt activate software-ul trebuie sa poata diferentia sursele de intrerupere.

4.3 Modul Multi-Master (Firmware)

In modul mulit-Master , generarea intreruperii la detectia conditiilor de START si STOP permite determinarea momentului cand bus-ul est liber.Bitii de START si STOP sunt resetati prin RESET sau cand modulul SSP este dezactivat.Controlul bus-ului I2C poate fi obtinut cand bitul P (SSPSTAT <4>)este setat,sau bus-ul este idle cu bitii de start si stop resetati.

Cand bus-ul este ocupat ,activarea intreruperii SSP va genera o intrerupere cand

conditia de stop apare.In operatiile multi-master SDA trebuie monitorizata pentru a vedea daca nivelul liniei este cel care se asteapta sa fie.Aceasta verificare trebuie facuta doar cand iesirea este pe 1 logic.Daca 1 logic este asteptat si este detectat 0 logic dispozitivul trebuie sa elibereze linia SDA si SCL (setare biti in TRIS)

Iata doua conditii in care arbitrarea poate fi pierduta:

. transferul adresei

. transferul datei

Cand logica slave-ului este activata , slave-ul continua sa receptioneze.

Daca arbitrarea a fost pierduta in timpul transferului adresei,comunicarea cu dispozitivul poate fi in desfasurare.Daca este adresat va fi generat un ACK

Daca arbitrarea a fost pierduta in timpul transferului de date ,dispozitivul va fi nevoit sa retransfere datele mai tarziu.

4.4 Operatiile Sleep

O potrivire de adresa sau un transfer al unui octet ,procesorul iese din starea de sleep(daca intreruperea SSP este activata).

4.5 Efectele unui reset

Un reset dezactiveaza modulul SSP si termina transferul curent.

5 Initializarea

Example 15-2: Initializarea SPI Mod Master

CLRF STATUS ; selectare Bank 0

CLRF SSPSTAT ; SMP = 0, CKE = 0, si reset biti de stare

BSF SSPSTAT, CKE ; CKE = 1

MOVLW 0x31 ; setare mod Master, CLK/16,

MOVWF SSPCON ; transmitere front descrescator (CKE=1 & CKP=1)

; Data sampled in middle (SMP=0 & Mod Master)

BSF STATUS, RP0 ; selectare Bank 1

BSF PIE, SSPIE ; activare intrerupere SSP

BCF STATUS, RP0 ; selectare Bank 0

BSF INTCON, GIE ; activare intreruperi

MOVLW DataByte ; data de transmis

;se poate muta data dintr-o locatie din RAM

MOVWF SSPBUF ; start transmisie

5.1 Modulul SSP / Compatibilitatea modulului SSP

Cand se face trecerea de la modulul Basic SSP ,SSPSTAT contine doi biti adtionali de control.Acesti biti sunt utilizati doar in modul SPI:

. SMP, SPI momentul de esantionare a datei de intrare

. CKE, SPI selectia frontului pentru clock

Pentru comatibilitate cu SPI a modulului Basic SSP , acesti biti trebuie configurati corespunzator.

Daca acesti biti nu sunt in starile aratate in tabelul 15-4

,pot aparea erori in comuni

catie.

6 Indicii de design

Intrebarea 1: Folosind modul SPI,nu reusesc sa comunic cu un dispozitiv SPI

Raspuns 1: Asigurati-va ca folositi modul SPI corect pentru acel dispozitiv.

Acest SPI suporta toate cele 4 moduri SPI deci ar trebui sa functioneze.Verificati polaritatea si faza clock-ului.

Intrebarea 2: Folosind modul I2C,nu reusesc sa fac sa functioneze modul master.

Raspuns 2:Acest modul SSP nu are mod master implementat hardware.

Vedeti nota de aplicatie AN578 pentru software care foloseste modulul SSP pentru a implementa modul master.

for devices that have the Master SSP module.

Intrebarea 3 Folosind modul I2C,scriu date in SSPBUF ,dar data nu este transmisa.

Raspuns 3:Asigurati-va ca ati setat CKP pentru eliberarea liniei de clock.

7 Note de aplicatii

Aceasta sectiune prezinta notele de aplicatie care sunt inrudite cu subiectul curent.

Titlu nota de aplicatie #

Use of the SSP Module in the I 2 C Multi-Master Environment. AN578

Using Microchip 93 Series Serial EEPROMs with Microcontroller SPI Ports AN613

Software Implementation of I 2 C Bus Master AN554

Use of the SSP module in the Multi-master Environment AN578

Interfacing PIC16C64/74 to Microchip SPI Serial EEPROM AN647

Interfacing a Microchip PIC16C92x to Microchip SPI Serial EEPROM AN668

Copyright © 2025 - Toate drepturile rezervate